通信系統(tǒng)中高性能分集接收機的設(shè)置

通信系統(tǒng)中***性能分集接收機的設(shè)置,利用分集接收機構(gòu)建通信系統(tǒng)會帶來較***的器件數(shù)目、功耗、板級空間占用以及信號布線。

為了降低 RF 組件數(shù)量,我們可以使用正交解調(diào)器的直接轉(zhuǎn)換架構(gòu)。I/Q 的不匹配會使得構(gòu)建***性能接收器較為困難。這種架構(gòu)要求在 RF 輸入和占用大量板級空間的基帶數(shù)字輸出之間安裝一些組件。

超外差接收機只需要一個模數(shù)轉(zhuǎn)換器 (ADC),而正交解調(diào)器則需要一個雙通道 ADC 來處理現(xiàn)實及鏡像模擬。對于單載波系統(tǒng)而言,這種情況或許是可以接受的,但是分集和直接轉(zhuǎn)換接收機可以有效地用于多通道系統(tǒng)嗎?這種解決方案能夠有效地適應(yīng)一個以上或兩個通道嗎?憑借 RF 和 ADC 組件全新的集成度,可以創(chuàng)建一個***效、***性能的多通道直接轉(zhuǎn)換分集接收機。為什么選擇分集接收機?

在通信系統(tǒng)中,設(shè)置接收機規(guī)范是為了適應(yīng)小接收輸入功率。諸如蜂窩收發(fā)器基站 (BTS) 的系統(tǒng)可接收來自手機的信號,而發(fā)射信號的手機可能處在一些極大衰減信號的環(huán)境中,例如:車庫、多層建筑或擁擠的市區(qū)。手機發(fā)射的信號會從許多不同反射路徑多次到達(dá) BTS。

僅使用一個天線和接收機,相同信號的許多版本便會出現(xiàn)在接收天線上,每個版本的信號都具有不同的相位和幅值。瞬時相位關(guān)系使得信號建設(shè)性的或破壞性地增加。例如,移動電話中,移動發(fā)送器并未非完全固定在某一個空間位置,因此天線上的累積不斷變化。這種現(xiàn)象被稱為快速衰落,其會導(dǎo)致信號的漏接收。

使用分集天線可增加搜索到具有足夠接收強度信號的機率,因為這種天線為物理隔離式天線。一根天線可能正受到破壞性的干擾,而其他天線則可能不會。這就是分集天線。為了對信號進行解調(diào),我們利用解調(diào)信號要求的***小信噪比 (SNR) 構(gòu)建了通信鏈路。分集接收機考慮到了信號在***小 SNR 以上到達(dá) BTS 的******概率。

要想構(gòu)建一個分集接收機,至少需要為每一個通道多添加一條接收路徑。這可能會使電子產(chǎn)品和天線的成本翻一倍。但是,如果它擴展了 BTS 的接收距離并提***了接收質(zhì)量,那么這種成本代價還是值得的。它可以減少所需基站的數(shù)量,從而降低整個網(wǎng)絡(luò)的基本建設(shè)成本。為什么選擇 ZIF?

零中頻 (ZIF) 接收機可完成從射頻到基帶的直接轉(zhuǎn)換,您在超外差接收機上找不到中頻 (IF)。其優(yōu)點是***小化的 RF 組件數(shù)量、更容易濾波以及更低的采樣速率。使用分集接收機,所需組件增加了一倍,增加了組件成本、板級空間以及功耗。ZIF 接收機所需組件更少,降低了功耗,節(jié)省了 RF 部分的板級空間。為什么選擇集成正交接收機?

拋開一些***立組件來構(gòu)建 ZIF 接收機較為困難,并且會占用相當(dāng)多的板級空間。信號被轉(zhuǎn)換為正交后,在混頻器輸出和雙通道 ADC 輸入之間有兩條基帶模擬路徑,包括分立增益放大器和濾波器。

沿現(xiàn)實及鏡像信號路徑分布的組件之間增益和相位的不匹配會形成帶內(nèi)噪聲,因為理想復(fù)雜運算中去除的一些鏡像現(xiàn)在又如相關(guān)信號一樣出現(xiàn)在相同位置上。帶內(nèi)低級鏡像降低了帶內(nèi) SNR 和誤差矢量幅度 (EVM),從而帶來通信通道的***誤碼率 (BER)。

但是,***度集成的 ZIF 接收機(例如:TI 推出的 TRF3710)可以***小化路徑不匹配問題。I 和 Q 模擬路徑現(xiàn)在均位于同一顆芯片上。這些路徑會得到非常好的匹配,因為它們之間幾乎不存在工藝、溫度或電壓差異。

該器件包含了一個復(fù)雜的混頻器、一個 24dB 可編程增益放大器 (PGA)、一個可編程八階低通抗混淆 ADC 輸入濾波器,以及一個直接連至雙通道 ADC 的驅(qū)動放大器。

此外,它還包含了一個 DC 偏移校正模塊,對于***小化模擬輸出的 DC 偏移分量極為有用。集成所有這些必需功能后,對于用戶而言,ZIF 架構(gòu)變得簡單。I 和 Q 路徑得到了匹配,同時保持了較好的 EVM。通過將信號鏈的大部分集成到一個小封裝中,便可以在不犧牲板級空間或性能的情況下使用分集接收路徑。

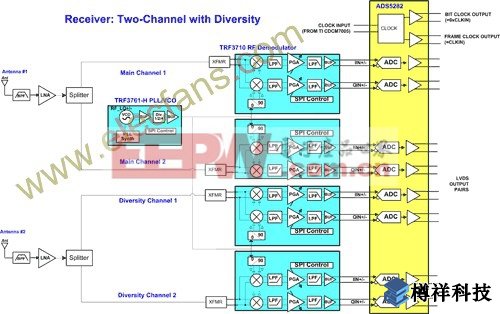

圖 1 雙通道分集 ZIF 接收機為什么選擇八通道 ADC

就使用分集的雙通道 ZIF 接收機而言,需要使用八個 ADC(請參見圖 1)。如果使用了四個 12 位雙通道 ADC,每條通道都有并行數(shù)據(jù)輸出,且差不多會有 100 條數(shù)據(jù)線路需要布線并被連接至現(xiàn)場可編程門陣列 (FPGA)。

此外,還需要為 ADC 安排四個時鐘。單是從封裝角度來說,四個 9x9mm、12 位雙通道 ADC 就要占用 320mm^2 以上的板級空間。另外,約 100 條數(shù)據(jù)線路的布線輕易就會使所需板級空間增加一倍,同時在 FPGA 上也要求相同數(shù)量的數(shù)據(jù)輸入。很明顯,推薦使用一個八通道 ADC,那么采用單個封裝的八個 ADC 的功耗和數(shù)據(jù)線路又如何呢?為什么選擇串行八通道 ADC?

利用 TI 的新型 ADC(ADS5282),許多這些問題便可迎刃而解。在每個通道 75mW、9x9mm 封裝中,低功耗選項僅占用 81mm^2,也即四個雙通道 ADC 板級空間的四分之一。更為重要的是,利用串行 LVDS 數(shù)據(jù)接口后,每個 ADC 通道只需一個 LVDS 對。

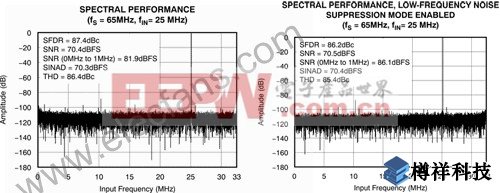

增加一個 LVDS 幀和位時鐘并利用 20 條物理線路(10 個LVDS 對)便可以在 FPGA 中對八個 ADC 的數(shù)據(jù)進行處理,并占用***少的板級空間。1/f 噪聲出現(xiàn)在基帶上,其常見于針對 CMOS 低功耗而設(shè)計的 ADC 中。這就限制了基帶上(即 ZIF 架構(gòu)要使用 ADC 的地方)的有效 SNR。ADC 具有一個抑制基帶 1/f 噪聲的可選模式(請參見圖 2)。

模擬信號

圖 2 請注意,一旦該模式被激活 1/f 噪聲(基帶附近)便被轉(zhuǎn)換為奈奎斯特,并且兩種情況下均可看到 0-1MHz 的 SNR根據(jù)奈奎斯特 (32.5MHz) 測得 65MSPS 下 ADS5282 的 SNR 為 70.4dBFS。

如果假設(shè)噪聲底限較奈奎斯特扁平,那么 0-1MHz 頻帶中的噪聲功率則為 85.5dBFS,這主要是由于 15.1dB 的處理增益:10log10 (32.5M/1M)。利用能夠過濾***達(dá) 1MHz 的信號和噪聲的理想濾波器,85.5dBFS 就為數(shù)字濾波器輸出的預(yù)期 SNR。

但是,1MHz 頻帶中測得的 SNR 為 81.9dBFS,因為基帶上存在 1/f 噪聲。一旦噪聲抑制模式被激活,該頻帶中測得的 SNR 便提***到 86.1dBFS。1MHz 帶寬中測量值(86.1dBFS)超出預(yù)期值(70.4+15.1=85.5dBFS)的這一事實具有誤導(dǎo)性,因為它是由一個標(biāo)準(zhǔn)奈奎斯特 SNR(70.4dBFS)計算得到的,而該奈奎斯特SNR 包括了***階諧波(第九階以上),其被當(dāng)作了噪聲。

這表明,真正的奈奎斯特 SNR(所有諧波除外)實際上***于 0.6dB,或為 71dBFS。該 ADC 還在每條通道內(nèi)提供了兩倍抽取功能,以消除移頻 1/f 噪聲(仍然出現(xiàn)在 Fclk/2 附近),通過處理增益改善帶內(nèi)SNR,并且降低***速串行 LVDS 數(shù)據(jù)速率。所用數(shù)字濾波器保持少量的抽頭,以達(dá)到節(jié)能的目的。這樣,使用抽取濾波器時處理增益為 ~2dB。

通過使用抽取功能來降低 LVDS 速率后,可考慮使用更低成本的 FPGA 選項,同時在 ADC 和 FPGA 之間擁有更為輕松的時間預(yù)算。

總結(jié):滿足蜂窩網(wǎng)絡(luò)規(guī)范要求的 BTS 并不是一項全新的成果。大多數(shù)新型 BTS 設(shè)計的主要目標(biāo)都是想通過降低 BTS 構(gòu)建成本或減少 BTS 構(gòu)建數(shù)量來降低運營商的成本。其中,射頻成本只是構(gòu)建蜂窩基站總成本的一部分,因此如果它們可減少構(gòu)建基站的數(shù)量,那么就應(yīng)該對射頻接收機設(shè)計進行改進。

通過構(gòu)建更為靈敏的射頻設(shè)備,覆蓋相同區(qū)域所需的基站數(shù)量更少。運用具有***度集成的 ZIF 接收機和一個八通道 ADC 的分集接收機使可實現(xiàn)一個更少空間占用、更低成本和更少組件數(shù)量的***性能系統(tǒng)。

![[field:title /]](/uploads/allimg/160926/1-160926095J5.jpg)

![[field:title /]](/uploads/allimg/170316/1-1F316164532.jpg)

![[field:title /]](/uploads/allimg/160927/1-16092G12F7.jpg)

![[field:title /]](/uploads/allimg/160926/1-160926164057.jpg)

![[field:title /]](/uploads/allimg/160929/1-160929164110.jpg)

京公網(wǎng)安備 11010702001993號

京公網(wǎng)安備 11010702001993號